Tang Nano 9k Fpga Gowin Gw1nr-9 Risc-v Hdmi

en 24 meses de

IVA incluido

Conoce los tiempos y las formas de envío.

Stock disponible

MercadoLíder | +50mil

- Tienes 30 días desde que lo recibes.

- Compra ProtegidaSe abrirá en una nueva ventana, recibe el producto que esperabas o te devolvemos tu dinero.

JELELECTRONICA

MercadoLíder Platinum

¡Uno de los mejores del sitio!

+50mil

Ventas concretadas

Brinda buena atención

Entrega sus productos a tiempo

Medios de pago

Meses sin Tarjeta

Tarjetas de crédito

¡Paga en hasta 3 cuotas!

Tarjetas de débito

Efectivo

Características del producto

Características principales

Marca | JELELECTRONICA |

|---|---|

Modelo | TANG NANO 9K |

Otros

Microcontrolador | GW1NR-9 |

|---|---|

Voltaje de funcionamiento | 3.3v a 5v |

Voltaje de entrada recomendado | 3.3v a 5v |

Voltaje de entrada límite | 3.3v a 5v |

Frecuencia del reloj | 27 MHz |

Capacidad de la memoria flash | 76 KB |

Capacidad SRAM | 8.19 MB |

Largo x Ancho x Altura | 7 cm x 2.6 cm x 1.1 cm |

Peso | 1 g |

Cantidad de entradas análogas | 1 |

Cantidad de pines digitales de entrada y salida | 1 |

Incluye cable USB | Sí |

Descripción

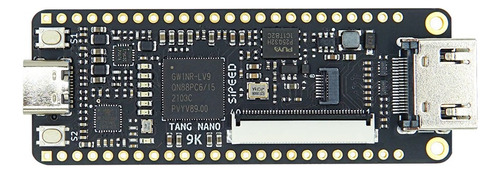

1. La Tang Nano 9K es una placa de desarrollo compacta basada en el chip FPGA Gowin GW1NR-9.

2. Su conector compatible con HDMI, conector de pantalla de interfaz RGB, conector de pantalla SPI, SPI FLASH y 6 LED permiten a los usuarios realizar fácil y rápidamente la verificación del FPGA, la verificación de núcleo suave RISC-V y la verificación del prototipo funcional.

3. La unidad lógica 8640 LUT4 propiedad de GW1NR-9 no solo se puede usar para diseñar varios circuitos lógicos complejos, sino que también puede ejecutar un núcleo suave PicoRV completo, que satisface las diversas necesidades de los usuarios para aprender FPGA, verificar el núcleo suave y en -diseño de profundidad.

4. Para Tang Nano 9K se desarrolla utilizando el software IDE de Gowin Yunyuan. Es compatible con el lenguaje de descripción de hardware general y puede realizar rápidamente trabajos relacionados, como llamar al núcleo de IP, síntesis de código, ubicación y enrutamiento, y generación de archivos de flujo de bits en el proceso de desarrollo de FPGA.

5. El chip BL702 incorporado para la placa de desarrollo Tang Nano9K proporciona descarga de USB-JTAG y funciones de depuración de USB-UART para GW1NR-9. Los usuarios solo necesitan usar el cable USB-C para conectar la placa de desarrollo a la computadora para completar la operación de descarga, sin la necesidad de comprar un descargador adicional y un cableado engorroso.

Configuración del núcleo:

Unidades lógicas (LUT4): 8640

Registro (FF): 6480

Memoria de acceso aleatorio estática distribuida SSRAM (bits): 17280

Bloquear memoria de acceso aleatorio estática B- SRAM (bits): 468K

Número de bloque de memoria estática de acceso aleatorio BSRAM (pcs): 26

Memoria flash de usuario (bits): 608K

PSRAM (bits): 64M

Módulo DSP de alto rendimiento: compatible con multiplicación de 9X9, 18X18, 36X36 bits y acumulador de 54 bits PLL)

Interfaz de pantalla de visualización: interfaz compatible con HDMI, interfaz de pantalla SPI e interfaz de pantalla RGB

Depurador: chip BL702 integrado, que proporciona descarga USB-JTAG y funciones de impresión de puerto serie USB-UART para GW1NR-9

IO: Admite 4mA, 8mA, 16mA, 24mA y otras capacidades de la unidad; proporciona Bus Keeper independiente, resistencias pull-up/pull-down y opciones de salida Open Drain para cada E/S

Conector: portatarjetas TF, 2 x 24P 2.54mm pin header pad

Teclas: 2 programables por el usuario teclas

LED: 6 LED programables integrados

Tamaño del producto: 70 x 26 mm

Color: Negro

Material: PCB+Metal

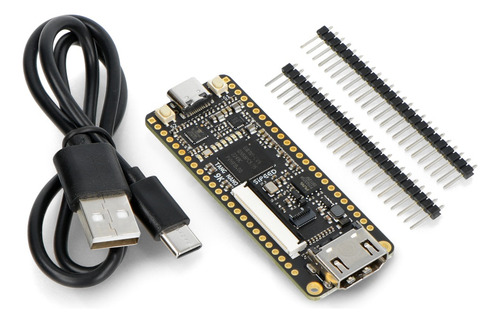

Contenido del paquete:

1 placa de desarrollo

2 cabezales de 2,54 pines

1 cable de datos

1 Estuche

Garantía del vendedor: 1 meses